EE220 2024 Noise Analysis and Simulation: Difference between revisions

No edit summary |

|||

| (5 intermediate revisions by the same user not shown) | |||

| Line 8: | Line 8: | ||

* What is the transistor's <math>g_m</math> and <math>V^*=\frac{2I_D}{g_m}</math>? | * What is the transistor's <math>g_m</math> and <math>V^*=\frac{2I_D}{g_m}</math>? | ||

Run a noise analysis from <math>1\mathrm{Hz}</math> to <math> | Run a noise analysis from <math>1\mathrm{Hz}</math> to <math>1\mathrm{THz}</math>. | ||

* Plot the drain current noise power spectral density, <math>\overline{i_{dn}^2 | * Plot the drain current noise power spectral density, <math>\frac{\overline{i_{dn}^2\left(f\right)}}{\Delta f}</math>. | ||

** Identify the regions where thermal noise and flicker noise dominates. | ** Identify the regions where thermal noise and flicker noise dominates. | ||

** What is the flicker noise corner? | ** What is the flicker noise corner? | ||

| Line 21: | Line 21: | ||

Change the length of the transistor to <math>2L_{\min}</math> and <math>3L_{\min}</math>. Identify and explain any changes in the drain current noise power spectral density. | Change the length of the transistor to <math>2L_{\min}</math> and <math>3L_{\min}</math>. Identify and explain any changes in the drain current noise power spectral density. | ||

* Repeat for the LVT and regular-VT NMOS transistors. Did you notice any differences in noise behavior? | |||

== Activity 2: PMOS Noise == | |||

Repeat Activity 1 but with 0.8V PMOS transistors with the same sizes, and with <math>V_{GS}=-0.4\mathrm{V}</math> and <math>V_{DS}=-0.4\mathrm{V}</math>. | |||

== Activity 3: Cascode Amplifier Noise Analysis == | |||

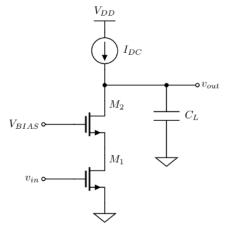

Consider the cascoded NMOS amplifier (biased with an ideal current source) shown in Fig. 1. Ignoring all other capacitances except <math>C_L</math>, and given the small-signal parameters <math>g_{m1}</math>, <math>g_{m2}</math>, <math>r_{o1}</math> and <math>r_{o2}</math>: | |||

{| | |||

| [[File:Cascode-noise.png|thumb|225px|Figure 1: A cascode amplifier.]] | |||

|- | |||

|} | |||

# Calculate the small-signal gain of the cascode amplifier, <math>A_v\!\left(s\right) = \frac{v_{out}}{v_{in}}</math>. Assume <math>g_{m1}r_{o1}\gg 1</math> and <math>g_{m2}r_{o2}\gg 1</math>. | |||

# Calculate the noise spectral density, <math>\overline{v^2_{out}\left(f\right)}</math>, and the total integrated output noise, <math>\overline{v^2_{out,T}}</math>. Assuming that <math>r_{o1}\rightarrow \infty</math> and <math>r_{o2}\rightarrow \infty</math>, and that the flicker noise is zero. | |||

# Repeat (2) but with finite <math>r_{o1}</math> and <math>r_{o2}</math>. How does this affect the output noise? | |||

== Activity 4: Input-Referred Noise == | |||

Given the gate-source capacitance, <math>C_{GS}</math>, of transistor <math>M_1</math> of the cascode amplifier in Fig. 1, calculate: | |||

* The input equivalent voltage noise generator, <math>\overline{v^2_{i,eq}\left(f\right)}</math>. | |||

* The input equivalent current noise generator, <math>\overline{i^2_{i,eq}\left(f\right)}</math>. | |||

Note that when calculating the output noise, you can assume that <math>r_{o1}\rightarrow\infty</math> and <math>r_{o2}\rightarrow\infty</math>, but when calculating the gains, assume finite <math>r_{o1}</math> and <math>r_{o2}</math>. | |||

== Report Guide == | |||

Write up a report (maximum of 5 pages including figures) answering the questions above. Include annotated graphs if needed. | |||

Latest revision as of 06:52, 9 October 2024

- Instructions: This activity is structured as a tutorial with an activity at the end. Should you have any questions, clarifications, or issues, please contact your instructor as soon as possible.

- At the end of this activity, the student should be able to:

- Perform noise simulations using Cadence Spectre using the GlobalFoundries 22nm FDSOI design kit.

Activity 1: NMOS Noise

Bias a 0.8V SLVT NMOS transistor with and . For a width of and a length of :

- What is the resulting DC drain current?

- What is the transistor's and ?

Run a noise analysis from to .

- Plot the drain current noise power spectral density, .

- Identify the regions where thermal noise and flicker noise dominates.

- What is the flicker noise corner?

- Estimate the value of .

- Estimate the value of

- What is the total integrated drain current noise power?

Recall that the MOSFET drain current noise can be modeled as:

Change the length of the transistor to and . Identify and explain any changes in the drain current noise power spectral density.

- Repeat for the LVT and regular-VT NMOS transistors. Did you notice any differences in noise behavior?

Activity 2: PMOS Noise

Repeat Activity 1 but with 0.8V PMOS transistors with the same sizes, and with and .

Activity 3: Cascode Amplifier Noise Analysis

Consider the cascoded NMOS amplifier (biased with an ideal current source) shown in Fig. 1. Ignoring all other capacitances except , and given the small-signal parameters , , and :

- Calculate the small-signal gain of the cascode amplifier, . Assume and .

- Calculate the noise spectral density, , and the total integrated output noise, . Assuming that and , and that the flicker noise is zero.

- Repeat (2) but with finite and . How does this affect the output noise?

Activity 4: Input-Referred Noise

Given the gate-source capacitance, , of transistor of the cascode amplifier in Fig. 1, calculate:

- The input equivalent voltage noise generator, .

- The input equivalent current noise generator, .

Note that when calculating the output noise, you can assume that and , but when calculating the gains, assume finite and .

Report Guide

Write up a report (maximum of 5 pages including figures) answering the questions above. Include annotated graphs if needed.