Installing the SkyWater 130nm Design Kit: Difference between revisions

No edit summary |

|||

| Line 20: | Line 20: | ||

== Using the PDK SPICE Models == | == Using the PDK SPICE Models == | ||

Once you have installed the PDK, we can now use [http://ngspice.sourceforge.net/ ngspice] to plot the transistor transfer and output characteristics. Let us use this | Once you have installed the PDK, we can now use [http://ngspice.sourceforge.net/ ngspice] to plot the transistor transfer and output characteristics. Let us use this [https://github.com/louisalarcon/ee220/blob/master/cidr/skywater-mos-test.sp SPICE deck]: | ||

<syntaxhighlight lang="text" line> | <syntaxhighlight lang="text" line> | ||

Revision as of 18:48, 20 July 2022

We will install the SkyWater 130nm design kit via the Open_PDKs scripts. This allows us to install (1) the Google/SkyWater SKY130 PDK from github and compile the timing files, (2) 3rd-party alphanumeric layout libraries, and (3) 3rd-party libraries for the xschem schematic entry and schematic capture tool.

Prerequisites

To install the files needed by the Magic layout tool, Magic must be installed. Download Magic here or via git:

git clone https://github.com/RTimothyEdwards/magic

Then follow the compile and install instructions.

Installing the PDK

After installing Magic, we can now download the PDK via:

git clone git://opencircuitdesign.com/open_pdks

See the full installation instructions at the Open_PDKs website.

Using the PDK SPICE Models

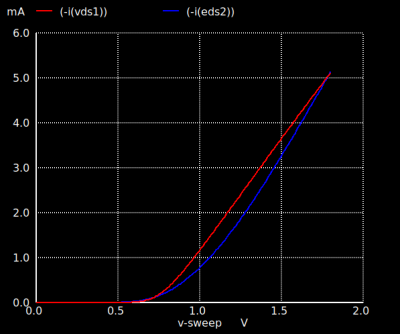

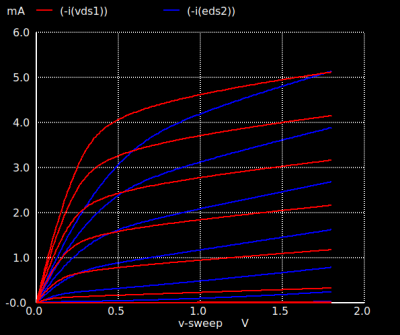

Once you have installed the PDK, we can now use ngspice to plot the transistor transfer and output characteristics. Let us use this SPICE deck:

1 * SKyWater 130nm Test Simulation

2

3 .option scale=1e-6

4 .lib /usr/local/share/pdk/sky130A/libs.tech/ngspice/sky130.lib.spice tt

5

6

7 xm01 d1 g1 0 0 sky130_fd_pr__nfet_01v8 l=0.15 w=10

8

9 vds1 d1 0 1.8

10 vgs1 g1 0 1.8

11

12 xm02 d2 g2 vdd vdd sky130_fd_pr__pfet_01v8 l=0.15 w=25

13 eds2 vdd d2 d1 0 1

14 egs2 vdd g2 g1 0 1

15

16 vsup vdd 0 1.8

17

18 .control

19 * Transfer Characteristics

20 dc vgs1 0 1.8 0.01

21 plot (-i(vds1)) (-i(eds2))

22

23 * Output Characteristics

24 dc vds1 0 1.8 0.01 vgs1 0.2 1.8 0.2

25 plot (-i(vds1)) (-i(eds2))

26

27 .endc

28

29 .end

Note that by default, the SkyWater 130nm design kit scales the width and length by , so the values entered are in microns. This is reiterated by the directive .option scale=1e-6 in line 3.

In Linux systems, by default, the installer places the SPICE models in /usr/local/share/pdk/sky130A/libs.tech/ngspice/sky130.lib.spice, and is called as a library in line 4. The tt directive indicates that we are using the typical corner.

When instantiating transistors, we use the x prefix, e.g. xm01 and xm02 since the model presents the transistors as subcircuits instead of native MOS transistors (usually instantiated using the m prefix). Line 7 instantiates the NMOS transistor sky130_fd_pr__nfet_01v8 with a length of and width of , while line 12 instantiates the PMOS transistor sky130_fd_pr__pfet_01v8 with a length of and width of .

We can then run NGSPICE from the command line:

$ ngspice skywater-mos-test.sp

We then get the following:

*****

** ngspice-37 : Circuit level simulation program

** The U. C. Berkeley CAD Group

** Copyright 1985-1994, Regents of the University of California.

** Copyright 2001-2022, The ngspice team.

** Please get your ngspice manual from http://ngspice.sourceforge.net/docs.html

** Please file your bug-reports at http://ngspice.sourceforge.net/bugrep.html

** Creation Date: Sun Jul 3 06:59:04 UTC 2022

******

Note: Compatibility modes selected: hs a

Warning: m=xx on .subckt line will override multiplier m hierarchy!

Circuit: * skywater 130nm test simulation

option SCALE: Scale is set to 1e-06 for instance and model parameters

option SCALE: Scale is set to 1e-06 for instance and model parameters

Doing analysis at TEMP = 27.000000 and TNOM = 27.000000

Reference value : 0.00000e+00

No. of Data Rows : 181

Doing analysis at TEMP = 27.000000 and TNOM = 27.000000

No. of Data Rows : 1629

ngspice 190 ->

Two plots are then generated: (1) the MOS transfer characteristics in Fig. 1, and (2) the MOS output characteristics in Fig. 2.