Design: A Simple Common-Source Amplifier: Difference between revisions

(→Part 1) |

|||

| Line 25: | Line 25: | ||

=== Part 1 === | === Part 1 === | ||

You are tasked to design a simple common-source amplifier biased with an ideal current source, with the following specifications: | You are tasked to design a simple common-source amplifier biased with an ideal current source, with the following specifications: | ||

* Small-signal low-frequency voltage gain: <math>\left|A_v\right| > 40</math> for an output DC voltage of <math>\frac{V_{DD}}{2} = 0.9\mathrm{V}</math>, and an output swing of at least <math>400\mathrm{mV}</math> (<math>\pm 200\mathrm{mV}</math> around <math>0.9\mathrm{V}</math> | * Small-signal low-frequency voltage gain: <math>\left|A_v\right| > 40</math> for an output DC voltage of <math>\frac{V_{DD}}{2} = 0.9\mathrm{V}</math>, and an output swing of at least <math>400\mathrm{mV}</math> (<math>\pm 200\mathrm{mV}</math> around <math>0.9\mathrm{V}</math>) | ||

* Unity-gain frequency: <math>f_u = 100\mathrm{MHz}</math> for a load capacitance <math>C_L=5pF</math> | * Unity-gain frequency: <math>f_u = 100\mathrm{MHz}</math> for a load capacitance <math>C_L=5pF</math> | ||

* <math>V^*=200\mathrm{mV}</math> | * <math>V^*=200\mathrm{mV}</math> | ||

Revision as of 08:51, 13 October 2022

- Instructions: This activity is structured as a tutorial with an activity at the end. Should you have any questions, clarifications, or issues, please contact your instructor as soon as possible.

- At the end of this activity, the student should be able to:

- Design a simple common-source amplifier.

Activity 1: Transistor Intrinsic Gain

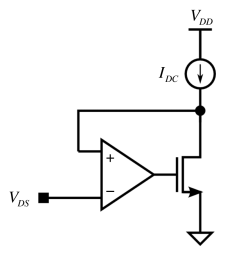

We can determine the intrinsic NMOS small-signal gain, , for a desired DC operating point, i.e for a given drain current, , and drain-to-source voltage, . This implies a certain gate-to-source voltage, . For square-law devices, we can easily calculate the required that corresponds to and . However, for deep submicron devices that do not follow the square law, we can either run simulations to determine this , or instead, we can let SPICE calculate for us. As seen in Fig. 1, we can use negative feedback to obtain the appropriate .

Using the circuit in Fig. 1, with , , , and the ideal amplifier gain, :

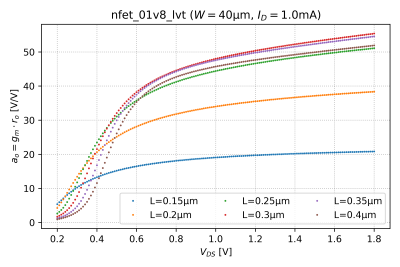

- Sweep from 200mV to 1.8V, and plot as a function of .

- From the vs. plot, derive the NMOS instrinsic gain, , as a function of .

- Repeat for transistor lengths of , , , , and , and generate the graphs in Fig. 2.

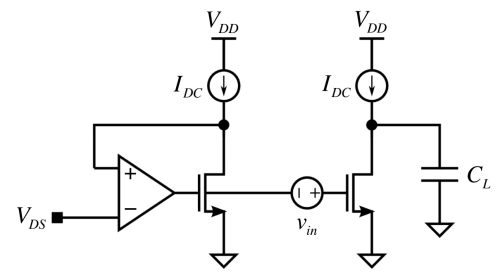

You can use a voltage-controlled voltage source (VCVS) to model the ideal amplifier. Aside from obtaining the intrinsic gain at different lengths, we can use this circuit as a replica bias generator, to generate the DC input voltage of a common-source amplifier using the same transistor, as shown in Fig. 3.

Design: A Common-Source Amplifier

Now that we have obtained the transistor (1) large-signal characteristics, i.e. the transfer and output characteristics, (2) the small-signal parameters, , , , and , and (3) the figures of merit, and , we can now put everything together and design a simple amplifier.

Part 1

You are tasked to design a simple common-source amplifier biased with an ideal current source, with the following specifications:

- Small-signal low-frequency voltage gain: for an output DC voltage of , and an output swing of at least ( around )

- Unity-gain frequency: for a load capacitance

You are to submit:

- A short description of the design procedure you used to obtain , , and .

- Any calculations you have done.

- A DC sweep of vs. .

- What is the maximum symmetric output voltage swing for ?

- What is the corresponding input voltage swing?

- A plot of the magnitude response showing the low frequency gain, and the unity-gain frequency.

- Are these your expected results?

Part 2

You now wish to test the technology and design an amplifier has the highest possible unity-gain frequency, while maintaining the voltage gain, for an output swing of at least , , and an output DC voltage of .

You are to submit:

- A short description of the design procedure you used to obtain , , , and .

- Any calculations you have done.

- A DC sweep of vs. .

- What is the maximum symmetric output voltage swing for ?

- What is the corresponding input voltage swing?

- A plot of the magnitude response showing the low frequency gain, and the unity-gain frequency.

- What is the maximum unity-gain frequency you achieved?

- How much more current are you consuming compared to the amplifier in Part 1?

Part 3

You are now asked to design an amplifier with the lowest possible DC power consumption, , while maintaining the voltage gain, for an output swing of at least , , and an output DC voltage of .

You are to submit:

- A short description of the design procedure you used to obtain , , , and .

- Any calculations you have done.

- A DC sweep of vs. .

- What is the maximum symmetric output voltage swing for ?

- What is the corresponding input voltage swing?

- A plot of the magnitude response showing the low frequency gain, and the unity-gain frequency.

- What is the maximum unity-gain frequency you achieved?

- How much more current are you consuming compared to the amplifier in Parts 1 and 2?

Report Guide

Write up a report (maximum of 5 pages including figures) answering the questions above. Include annotated graphs if needed.

Submission

This activity is for both graduate and undergraduate students. For UP students, the submission bin link will be posted in Piazza.