Activity: MOS Design Parameters: Difference between revisions

No edit summary |

|||

| (25 intermediate revisions by the same user not shown) | |||

| Line 19: | Line 19: | ||

|- | |- | ||

|} | |} | ||

=== Output Resistance === | === Output Resistance === | ||

| Line 34: | Line 32: | ||

|- | |- | ||

|} | |} | ||

Answer the following questions: | Answer the following questions: | ||

# Given the transconductance plot in Fig. 3, why is there a peak in the transconductance curve? What is causing this? | # Given the transconductance plot in Fig. 3, why is there a peak in the transconductance curve? What is causing this? | ||

# | # Generate Fig. 3, but on a logarithmic y-axis. Is this what you expect for <math>V_{GS}<V_{TH}</math>? Explain. | ||

# Plot <math>g_m</math> for <math>V_{DS}=0.45\mathrm{V}</math> and <math>V_{DS}=1.35\mathrm{V}</math>. Does the transconductance change with <math>V_{DS}</math>? Is this the behavior you expect? Explain. | |||

# Plot the output resistance for <math>V_{GS}=0.45\mathrm{V}</math> and <math>V_{GS}=0.1.35\mathrm{V}</math>. Do you see any changes in the the effects of process variations? What do you think is causing this behavior? | |||

== Activity 2: Power Efficiency == | == Activity 2: Power Efficiency == | ||

We can define a power efficiency figure of merit (FoM) for our transistors that quantifies the DC current cost, i.e. <math>I_D</math>, of achieving a certain transconductance, <math>g_m</math>. Mathematically, we can express this as <math>\frac{g_m}{I_D}</math>, and is plotted vs. <math>V_{GS}</math>, as shown in Fig. 6. | |||

{| | |||

| [[File:Nmos-1v8-lvt-L=150nm-gmoverid.png|thumb|400px|Figure 6: NMOS <math>\frac{g_m}{I_D}</math>.]] | |||

| [[File:Nmos-1v8-lvt-L=150nm-vov.png|thumb|400px|Figure 7: NMOS <math>V_{ov}=\frac{2\cdot I_D}{g_m}</math>.]] | |||

|- | |||

|} | |||

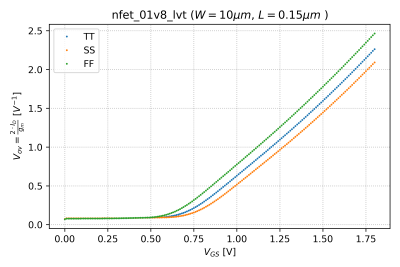

An alternative form of this power efficiency metric, is <math>V^*=V_{ov}=\frac{2\cdot I_D}{g_m}</math>. This alternative FoM is plotted against <math>V_{GS}</math>, as shown in Fig. 7. | |||

Answer the following questions: | |||

# Why does the plot <math>\frac{g_m}{I_D}</math>, shown in Fig. 6, flatten out at low <math>V_{GS}</math>? | |||

# Recreate Fig. 6 but with <math>L=0.20\mathrm{\mu m}</math> and <math>L=0.30\mathrm{\mu m}</math>. Does the maximum value of <math>\frac{g_m}{I_D}</math> change? Is this what you expect? Why or why not? | |||

== Activity 3: Aggregate Figure of Merit == | |||

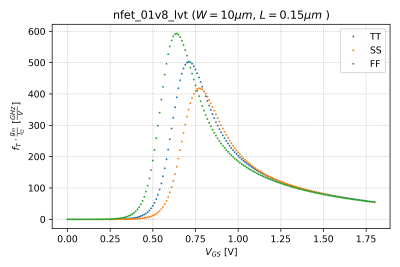

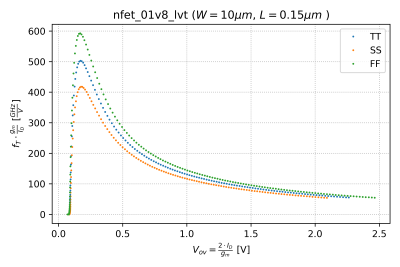

Increasing the power efficiency of the transistor moves it further into its subthreshold region, leading to lower transition frequencies. Thus, in choosing the value of <math>V^*</math>, we can define an aggregate figure of merit that takes into account both the power efficiency and transition frequency, as <math>f_T\cdot\frac{g_m}{I_D}</math>. This figure of merit is plotted against <math>V_{GS}</math>, as shown in Fig. 8. | |||

{| | |||

| [[File:Nmos-1v8-lvt-L=150nm-ftgmoverid.png|thumb|400px|Figure 8: NMOS <math>f_T\cdot\frac{g_m}{I_D}</math> vs. <math>V_{GS}</math>.]] | |||

| [[File:Nmos-1v8-lvt-L=150nm-ftgmoverid-vs-vov.png|thumb|400px|Figure 9: NMOS <math>f_T\cdot\frac{g_m}{I_D}</math> vs. <math>V_{ov}</math>.]] | |||

|- | |||

|} | |||

Notice that the peak occurs at different <math>V_{GS}</math> values over corners. However, if we plot it against <math>V^* = V_{ov}</math> as seen in Fig. 9, we get a consistent peak, at around <math>V^* \approx 200\mathrm{mV}</math>. | |||

Answer the following questions: | |||

# It seems that the peak <math>f_t\cdot \frac{g_m}{I_D}</math> occurs in the moderate inversion region. Plot this figure of merit for <math>L=0.20\mathrm{\mu m}</math> and <math>L=0.30\mathrm{\mu m}</math>. Does the peak still appear in the moderate inversion region? Is this what you expected? Why? | |||

# For <math>L=0.20\mathrm{\mu m}</math> and <math>L=0.30\mathrm{\mu m}</math>, does the peak occur at the same <math>V^*</math> over the FF, TT, and SS corners? Is this what you expected? Why? | |||

== Activity 4: PMOS Small Signal Parameters == | |||

Repeat Activities 1, 2, and 3 for a 1.8V LVT PMOS transistor with a width <math>W=10\mathrm{\mu m}</math>, a length <math>L=0.35\mathrm{\mu m}</math>, and with <math>nf=1</math>. When varying PMOS length, use <math>L=0.50\mathrm{\mu m}</math> and <math>L=0.70\mathrm{\mu m}</math>. | |||

== Report Guide == | |||

Write up a report (maximum of 5 pages including figures) answering the questions above. Include annotated graphs if needed. | |||

== | == Submission == | ||

This activity is for both graduate and undergraduate students. For UP students, the submission bin link will be posted in Piazza. | |||

Latest revision as of 08:25, 6 October 2022

- Instructions: This activity is structured as a tutorial with an activity at the end. Should you have any questions, clarifications, or issues, please contact your instructor as soon as possible.

- At the end of this activity, the student should be able to:

- Obtain the small signal design parameters of NMOS and PMOS transistors.

Activity 1: Small Signal Models

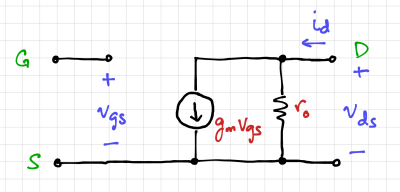

Most of the time, we are interested in the small signal behavior of our amplifiers, i.e. what happens to the amplifier voltages and currents as we introduce small disturbances (information carrying signals) at the input. To gain intuition and to facilitate circuit analysis using nonlinear devices, we linearize our circuits to obtain the two-port model shown in Fig. 1. For MOSFETs at low frequencies, the two-port model is composed of the transconductance, and the output resistance.

Transconductance

Transconductance is defined as:

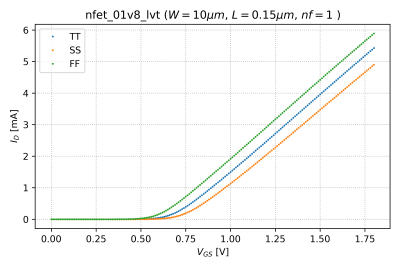

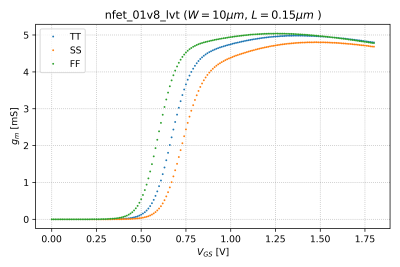

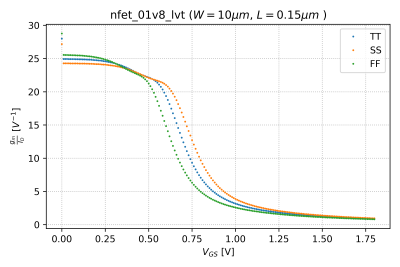

This is the slope of the transfer characteristic curves. Thus, by numerically differentiating the vs. curve shown in Fig. 2 for an NMOS transistor with a width , a length , and with , we can obtain the transconductance plot shown in Fig. 3.

Output Resistance

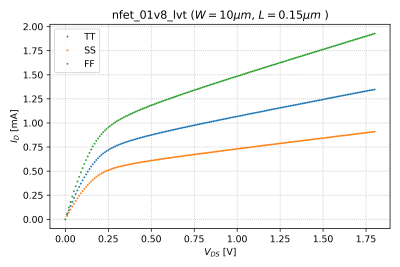

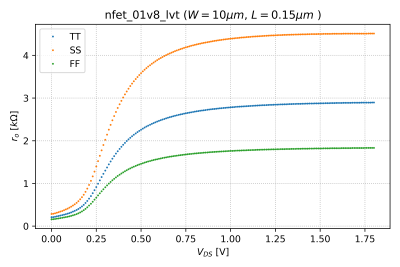

Similarly, we can take the derivative of the output characteristics, shown in Fig. 4 for , to get the output resistance, which is defined as:

The output resistance as a function of is shown in Fig. 5 for .

Answer the following questions:

- Given the transconductance plot in Fig. 3, why is there a peak in the transconductance curve? What is causing this?

- Generate Fig. 3, but on a logarithmic y-axis. Is this what you expect for ? Explain.

- Plot for and . Does the transconductance change with ? Is this the behavior you expect? Explain.

- Plot the output resistance for and . Do you see any changes in the the effects of process variations? What do you think is causing this behavior?

Activity 2: Power Efficiency

We can define a power efficiency figure of merit (FoM) for our transistors that quantifies the DC current cost, i.e. , of achieving a certain transconductance, . Mathematically, we can express this as , and is plotted vs. , as shown in Fig. 6.

An alternative form of this power efficiency metric, is . This alternative FoM is plotted against , as shown in Fig. 7.

Answer the following questions:

- Why does the plot , shown in Fig. 6, flatten out at low ?

- Recreate Fig. 6 but with and . Does the maximum value of change? Is this what you expect? Why or why not?

Activity 3: Aggregate Figure of Merit

Increasing the power efficiency of the transistor moves it further into its subthreshold region, leading to lower transition frequencies. Thus, in choosing the value of , we can define an aggregate figure of merit that takes into account both the power efficiency and transition frequency, as . This figure of merit is plotted against , as shown in Fig. 8.

Notice that the peak occurs at different values over corners. However, if we plot it against as seen in Fig. 9, we get a consistent peak, at around .

Answer the following questions:

- It seems that the peak occurs in the moderate inversion region. Plot this figure of merit for and . Does the peak still appear in the moderate inversion region? Is this what you expected? Why?

- For and , does the peak occur at the same over the FF, TT, and SS corners? Is this what you expected? Why?

Activity 4: PMOS Small Signal Parameters

Repeat Activities 1, 2, and 3 for a 1.8V LVT PMOS transistor with a width , a length , and with . When varying PMOS length, use and .

Report Guide

Write up a report (maximum of 5 pages including figures) answering the questions above. Include annotated graphs if needed.

Submission

This activity is for both graduate and undergraduate students. For UP students, the submission bin link will be posted in Piazza.