Activity 7: Difference between revisions

Jump to navigation

Jump to search

(Created page with "Exercise on Timing. A single pipeline processor operating at 1V is depicted in the figure below: a. Propose a 3-pipe stage version. Justify your solution. What would be the maximum clock period allowed for the single stage and 3-stage versions? b. Discuss how moving from single stage to 3-pipe stage affects the energy of the processor.") |

No edit summary |

||

| Line 3: | Line 3: | ||

A single pipeline processor operating at 1V is depicted in the figure below: | A single pipeline processor operating at 1V is depicted in the figure below: | ||

[[File:Timing-pipeline.PNG]] | |||

a. Propose a 3-pipe stage version. Justify your solution. What would be the maximum clock period allowed for the single stage and 3-stage versions? | |||

b. Discuss how moving from single stage to 3-pipe stage affects the energy of the processor. | b. Discuss how moving from single stage to 3-pipe stage affects the energy of the processor. | ||

Revision as of 15:30, 4 December 2023

Exercise on Timing.

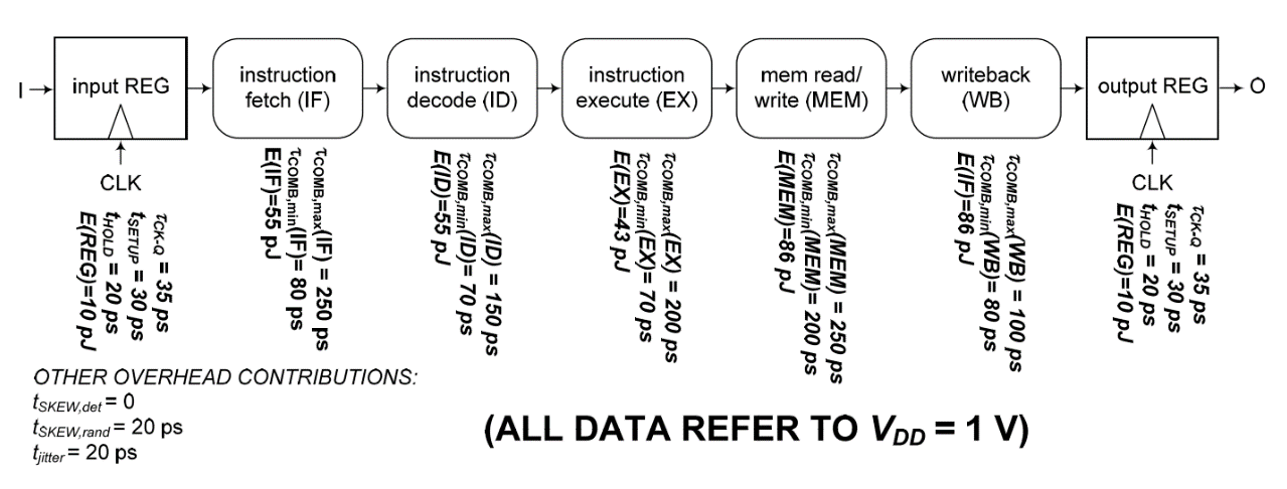

A single pipeline processor operating at 1V is depicted in the figure below:

a. Propose a 3-pipe stage version. Justify your solution. What would be the maximum clock period allowed for the single stage and 3-stage versions?

b. Discuss how moving from single stage to 3-pipe stage affects the energy of the processor.